Genie reduced number of wishes to 0. But by doing so he granted one of the wishes, so it became -1 (255).

- 39 Posts

- 134 Comments

341·9 months ago

341·9 months agoI don’t know. If the poster couldn’t be bothered to fact-check, why would I? It is just safer to assume that it can be misinformation.

Both antecedent and consequent are sampled at preponed region. So assertion will not trigger at the edge where adc_data_en rises. This is the intention, since the value of adc_data or adc_data_en do not matter at the edge where adc_data_en rises, but they do matter in the following edge where the D for the flops calculated based on adc_data and adc_data_en are registered. All these are assuming adc_data_en and adc_data are synchronous to the clock. Edit: Adding to this, if you want adc_data_en to be evaluated in observed region, you can do something like this: property(@(posedge clk) disable iff (!adc_data_en) adc_data==true_data); However I would not recommend this. One reason is that, at the cycle where adc_data_en falls this checker will not fire, but it probably should. Second reason is that, at the edge where adc_data_en rises, this assertion may work in RTL sim with no timing delays or hold/setup time, but it will fail in a realistic gatevlevel simulation. As a rule of thumb synchronous signals should be used inside property where they are evaluated in preponed region.

You can use auxiliary code. It is usually more readable and less error prone that multi-trigger assertions. Something like: always @(negedge adc_sample) true_voltage <= input_channel; assert property(@(posedge clk) adc_data_en |-> adc_data == true_voltage); Note that behaviour is not completely equivalent, for example as long as adc_data_en is highassertion will keep matching, not only once when adc_data_en rises. If you want thevoriginal behaviour you can use $rose(adc_data_en). Auxiliary code also makes it easier for 20 delay case. For example you can clock the always block with posedge clock and use a 20-size shift-register which is conditionally enabled if adc_data_en in low. I am not sure of the intended behaviour so take it with a grain of salt.

That’s like saying a bus driver’s job is to turn a steering wheel.

That’s a good analogy, I will use that.

1·1 year ago

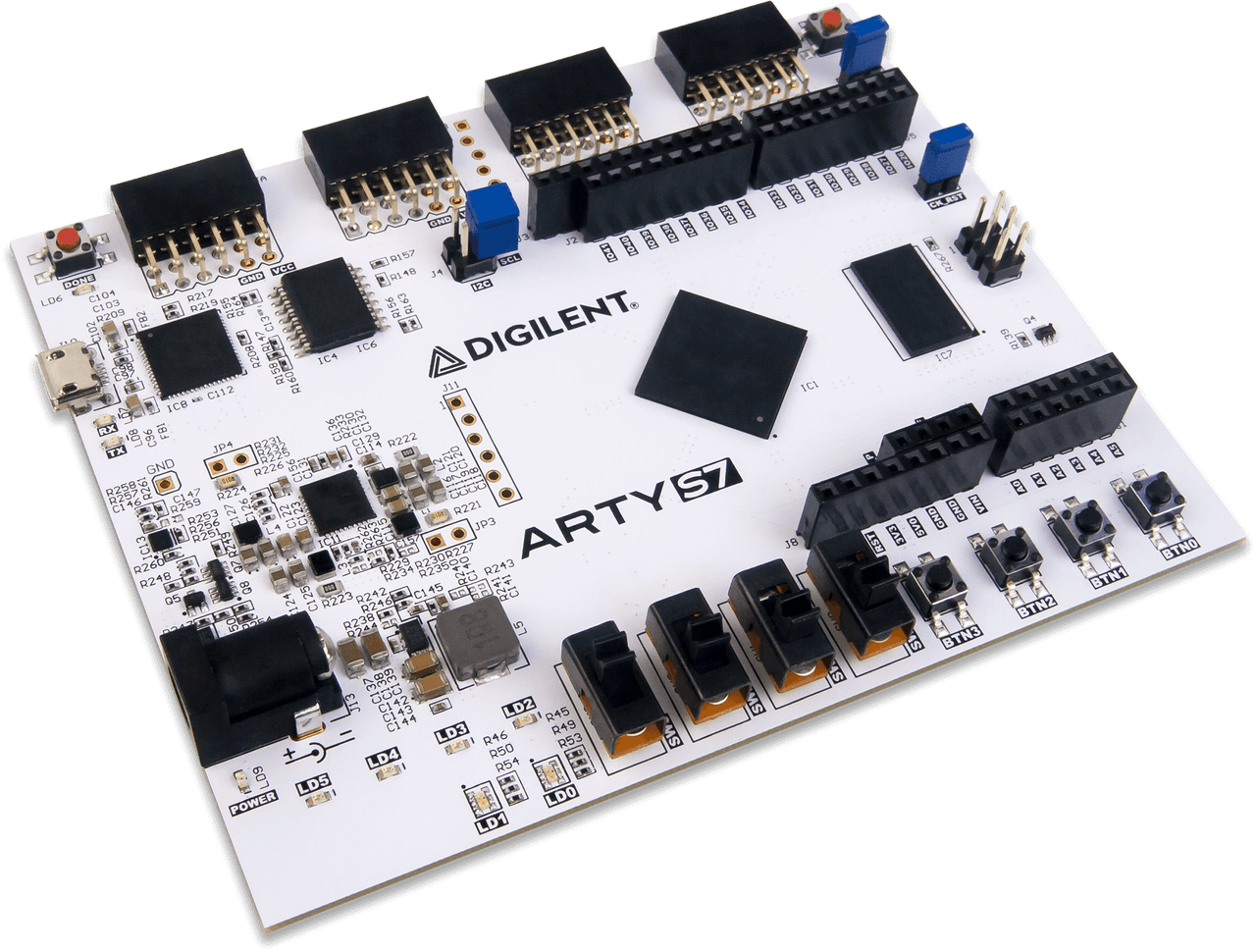

1·1 year agoIt is not much about the voltage level but high frequency current activity. Current can cause voltage drop on parasitic resistance and inductance of the breadboard, jumpers, connections, passive components etc. and can cause supply of the chip to be non-ideal or ripple. Your power source is a battery and not a switching power supply, so power will be cleaner, which is good. The chip also doesn’t consume high current, and its output is 32khz clock, fairly low frequency. So I wouldn’t worry so much about decoupling.

2·1 year ago

2·1 year agoDecoupling capacitor is there to filter out hogh frequency ripples from the lower supply. It is very hard for the consumer to know the high frequency current consumption of the chip, and its effects on the chip. Therefore decoupling is something where you should always follow the datasheet recommendation. As others said, ceramic capacitor has lower series resistance and inductance, which makes it the better choice for decoupling. Follow the instructions on layout as well, which usually says that decoupling capacitor should be as close as possible to the chip and grounded well. That being said, if you are prototyping on a breadboard, series inductance of a capacitor may not be your biggest concern, as breadboard connections will have that too. You can also still try to get your circuit working with the capacitor you have while waiting for ceramic one, chances are any capacitor will work good enough.

Isn’t it the opposite? Sun is rising late, so less likely to be woken up by sun (if that’s the joke).

27·1 year ago

27·1 year ago“Terrorism” has had a very loose definition in Turkey for years. Pretty much any anti-government activity or criticism can be labelled as such.

An emergency alert went off on my wife’s phone for a second time at 2.50, and 26 minutes later I still couldn’t fall asleep. I am also anxiously waiting for my alarm to ring any time. I don’t want to disable emergency alarms because they are important, but if they keep sending them in the middle of the night again and again at different hours they aren’t leaving me much choice.

Water drips on the way from the lake, not towards the lake.

31·2 years ago

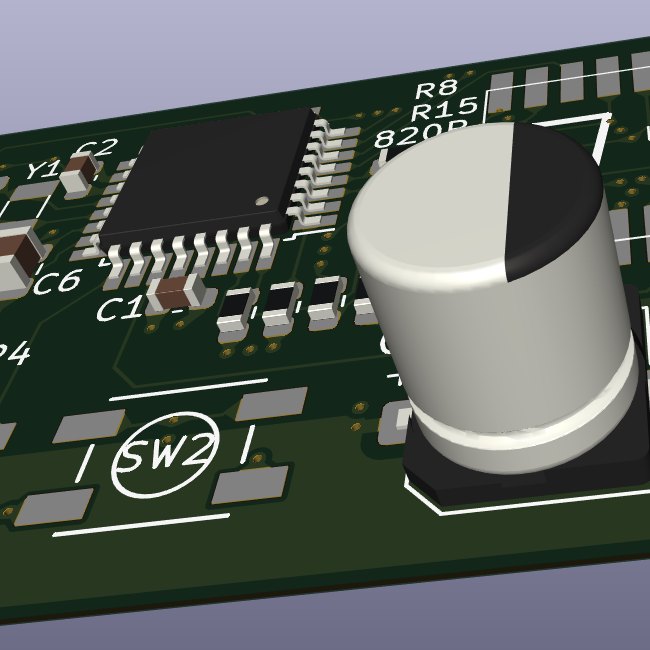

31·2 years agoHold a small piece of metal (paper clip?) between solder pads with a tweezer. Heat up tip of a metal fork/spoon (Sharp edge of fork could work better) on a stove. Take it from stove and use it immediately to melt the solder on one pad (seems like there is already enough solder there). I am not sure if it would work but maybe worth trying. Heating entire fork could be hard, so maybe something with smaller metal mass could work better, like a screwdriver, nail clipper etc).

DC motors have high inductance, meaning that the current going over it will resist to change. When you turn off a pair of nmos, current will likely start flowing over the the other pair, from source to drain. Depending on the spec of your nmos, you may consider using diodes in parallel to nmos to carry this current. Obviously these diodes should be reverse biased during normal operation.

3·2 years ago

3·2 years agoNot answering the question but if you studied in English outside of the UK it may be enough. But you need to certify that you studied in English through https://www.ecctis.com/visasandnationality . That is how I did it, and I think it is easier and can be quicker.

1·2 years ago

1·2 years agoPaywall

In my first ever programming class textbook was using Allman. Probably for this reason, it is easy for a beginner to match braces. It is a lot loss common industry to my knowledge.

Vizier is queen, isn’t it?